# CS-473 Embedded System

# Lab Report 4.0

# LT24 LCD Controller Implementation

Students: Chuanfang Ning 320662 Alexander Sigrist 296025 The collaborating group: Aliaa Diab 302713 Raphael Linsen 322834

| Introduction                                 | 3  |

|----------------------------------------------|----|

| Problem statement                            | 3  |

| System Diagrams                              | 3  |

| Full System Block Diagram                    | 3  |

| Custom IP Block Diagram                      | 4  |

| Slave Register Interface                     | 4  |

| LCD Sequencer                                | 5  |

| FIFO                                         | 6  |

| DMA Master Controller                        | 7  |

| Custom IP finite state machine (FSM) diagram | 8  |

| LCD Sequencer State Machine                  | 8  |

| Timing Diagrams                              | 8  |

| DMA Master State Machine                     | 11 |

| Sub-State Machine of DMA Burst Transfer      | 11 |

| Custom IP register map                       | 12 |

| Top-level block diagram Hardware connection  | 12 |

| Memory Organization                          | 13 |

| LT24 Control                                 | 14 |

| LT24 Register Initialisation                 | 14 |

| LT24 Data Transfer                           | 15 |

| Conclusion                                   | 16 |

| References                                   | 16 |

# Introduction

### Problem statement

In Lab 3.0, the goal is to propose a detailed design for an FPGA-based system which can interface with an LT24 LCD display by Terasic. The design will include a master unit that can initiate transfers on the Avalon bus to fetch image data frames from memory. This LT24 sub-system will later be combined with a sub-system developed by another team that handles reading image data from a TRDB-D5M camera to memory. In order to ensure compatibility and functionality of the full-system, the shared memory resource must be agreed upon and specified in detail.

# System Diagrams

## Full System Block Diagram

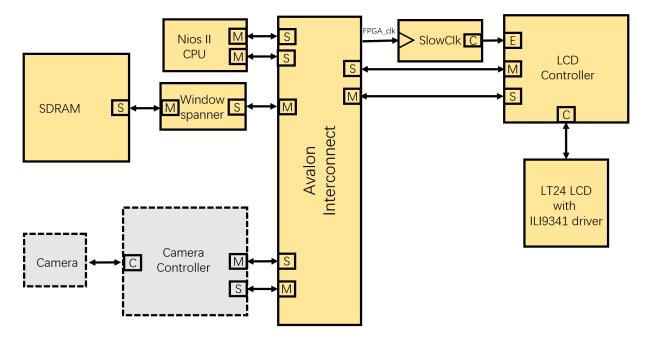

A SlowClk module, identical to that used in Lab 2.2, will be added to divide the 50 MHz FPGA\_clk signal by 4. This will produce a 12.5 MHz clock with a period of 80 ns that will allow the LCD controller submodule FSM to generate low-level 8080-I MCU parallel interface signals with the correct timings.

## Custom IP Block Diagram

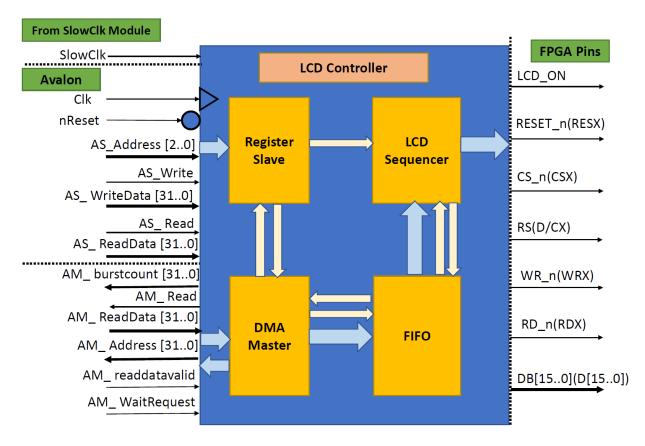

The custom LCD controller IP block is composed of 4 submodules as shown in the figure below: An Avalon slave memory-mapped register interface for programming, an LCD sequencer to send commands and RGB signals, a FIFO (implemented using the included IP block in Quartus) and a Master Controller which implements the DMA functionality.

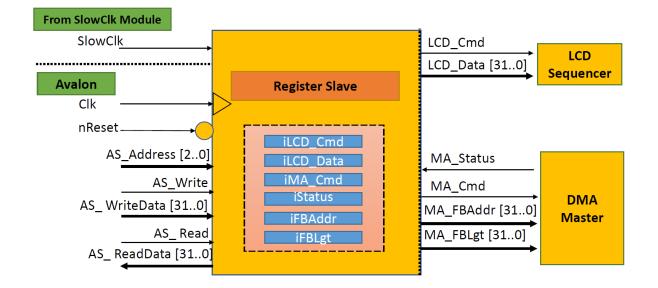

#### Slave Register Interface

This block includes an Avalon slave interface which allows the Custom LCD Controller to be programmed by the NIOS II Softcore CPU. All the information about available registers and their addresses are listed in the <u>Custom IP register map</u>. The SlowClk is connected to the Avalon slave register interface submodule. The LCD\_Cmd signal will be asserted to the desired value written from the Avalon interface by the NIOS II processor for one SlowClk cycle. Similarly, the MA\_Cmd signal will be asserted for one FPGA clk cycle. This allows the command to trigger the respective FSMs to do a 'single-shot' execution of an FSM cycle that returns to an idle state. More details in <u>Custom IP finite state machine (FSM) diagram</u>.

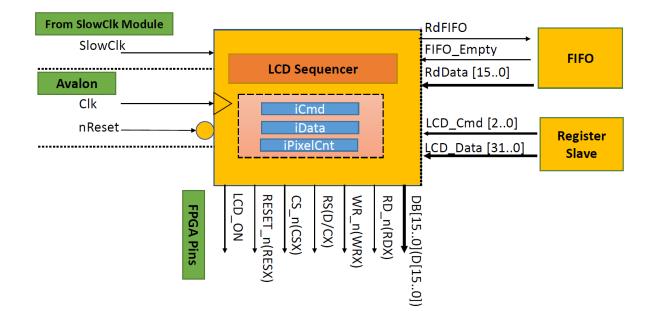

#### LCD Sequencer

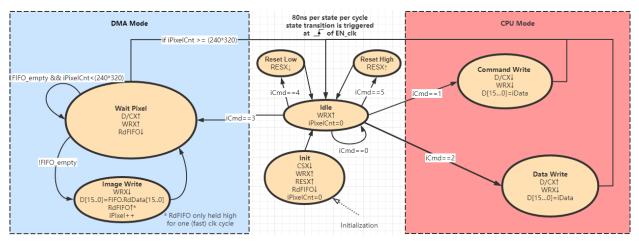

The LCD sequencer submodule is responsible for generating the 8080-I 16b parallel bus MCU interface signals with the correct timing required to communicate with the ILI9341 IC. This controller will have several different modes, which are switched according to the LCD\_Cmd register.

"CPU mode" will be for configuration where the LCD controller submodule will set configuration registers (register address/command then register data/parameters) in the ILI9341 on startup and reset as well as before each new image frame. It is also responsible for hard resetting the ILI9341 by toggling RSX pins. There are 4 sub-modes in the "CPU mode" which respectively send command address, send command data, and set or reset the RESX signal to the ILI9341. Which sub-mode to enter is controlled by asserting the value of LCD\_Cmd (valid values are 1, 2, 4, 5).

When the value of LCD\_Cmd is asserted to 3 by the Register Slave, the LCD sequencer enters "DMA mode", in which it will automatically dequeue an image data frame from the FIFO and write it to the LCD.

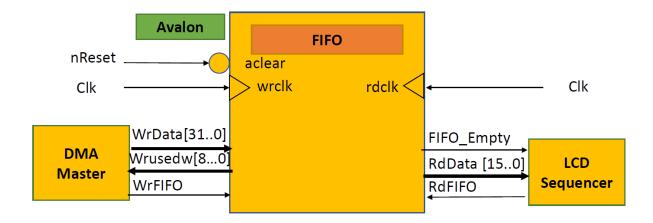

#### FIFO

The FIFO is configured with a size of 256 words; it was sized to store the results of several burst transfers and to efficiently use the full size of the allocated 10kb memory block in the FPGA. The FIFO is configured to have separate read and write clocks with 32b write width and 16b read width. This will allow the DMA Master to write words from memory (composed of two 16b doublet RGB pixels each) into the FIFO and the LCD sequencer to read 16b RGB pixels from the FIFO in an efficient manner. The used words (wr*usedw[]*), with an additional bit to prevent roll-over, will be exported from the write side as an input to the DMA Master Controller to check if there is sufficient space in the FIFO to store the data from a burst-read from memory. The *empty* signal will be exported on the read side to tell the LCD controller if there are still pixels in the FIFO to read and display. The FIFO is configured in show-ahead synchronous mode so that data appears before the assertion of RdData signal, thus the LCD Sequencer doesn't need to wait for the data to be available to read from FIFO. The aclear register of FIFO should also be configured to implement an asynchronous reset so that the pixel data is cleared in the case of a reset and the system begins from a valid initial state. The FIFO's FPGA resource usage is presented in the figure below:

| Resource Usage   |

|------------------|

| 1 lut + 1 M10K + |

| 89 reg           |

**FIFO Resource Usage**

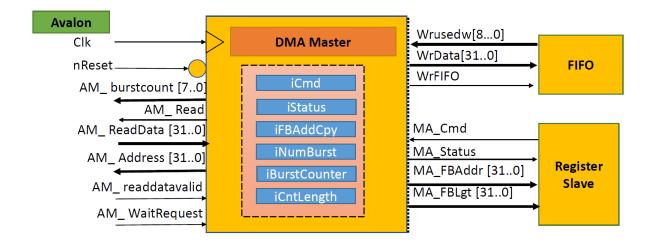

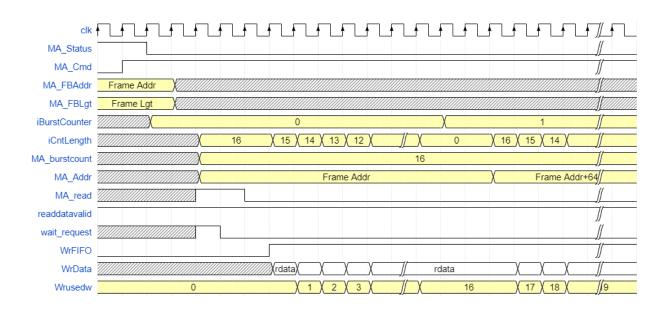

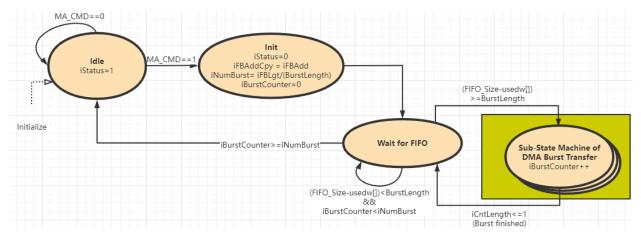

#### DMA Master Controller

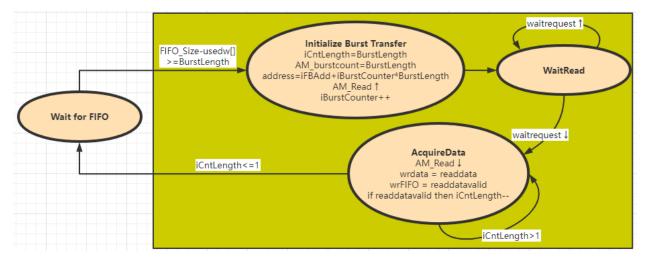

The DMA Master Controller consists of an Avalon master interface that can initiate transfers on the Avalon bus. It is responsible for fetching data from the SDRAM and writing it into the FIFO using burst transfers of 16 word lengths. It checks the wr*usedw[]* signal from the FIFO to ensure there is enough free space to store the data from the burst transfer. This master controller unit is configured using the slave register interface where it gets a starting address of the image frame buffer in memory (MA\_*FBAdd*), the length of the data buffer (MA\_*FBLgt*) and a signal (MA\_Cmd) to start. It performs a total number of  $\frac{320 \times 240 \text{ px}}{16 \text{ words/burst} \times 2 \text{ px/word}} = 2400 \text{ burstreads for}$  one frame. At the start of each burstread, it initializes the address and burstcount. At the start of each burst it increments the address and decrements the burst of the NIOS II processor will poll to determine if the operation is complete. When the operation is complete, the NIOS II will set the FbAddr and FBLgt for the next buffer and start the DMA and the LCD sequencer again.

## Custom IP finite state machine (FSM) diagram

The state machine for the LCD Sequencer is presented below. There are two main operating modes "CPU mode" to perform startup/reset sequence commands (address and data) and "DMA mode" to send RGB data from the FIFO to the ILI9341.

#### LCD Sequencer State Machine

#### **Timing Diagrams**

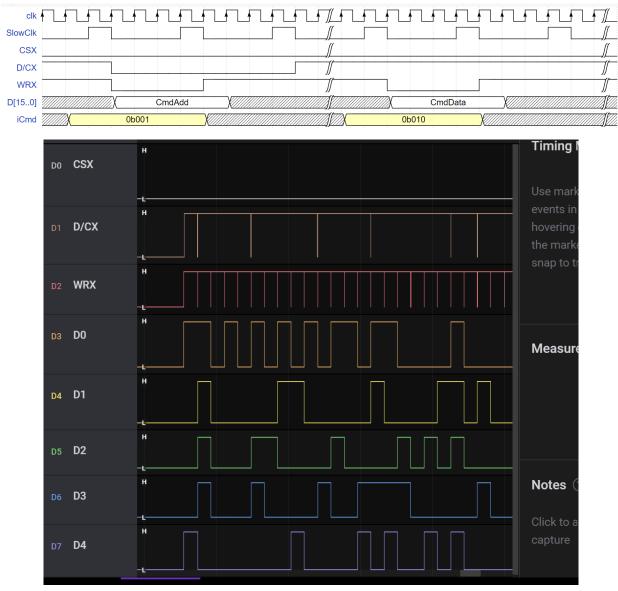

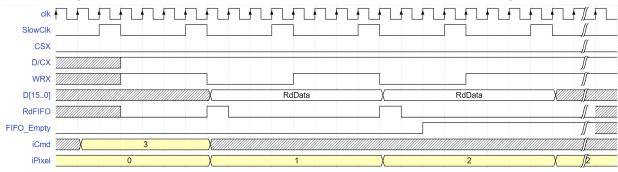

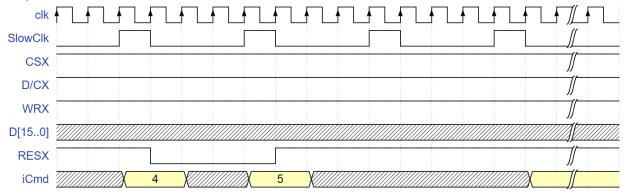

The waveform of Signals in "DMA Mode" and "CPU Mode" are shown below to help understand the FSM of LCD Sequencer.

The following waveform shows the **command address writing** and **command data writing** in "CPU mode" of the LCD Sequencer in design and test:

The following waveform shows the "DMA mode" of the LCD Sequencer in design and test:

| DO CSX       | <u>н</u> |  |  |

|--------------|----------|--|--|

| D1 D/CX      | -H       |  |  |

| D2 WRX       | -H       |  |  |

| D3 <b>D0</b> | H<br>-L  |  |  |

| D4 D1        | H<br>-L  |  |  |

| D5 <b>D2</b> | -н       |  |  |

| D6 D3        | -H       |  |  |

| D7 <b>D4</b> | н<br>-L  |  |  |

The following waveform shows the **set** and **reset** of the ILI9341 in "CPU mode" of the LCD Sequencer:

The following waveform shows the timing of the DMA Master:

#### DMA Master State Machine

#### Sub-State Machine of DMA Burst Transfer

| Addr. | Write register | Writedata[310] | Read register | Readdata[310] | Description                                                                                                  |

|-------|----------------|----------------|---------------|---------------|--------------------------------------------------------------------------------------------------------------|

| 0     | LCD_Cmd        | →iLCD_Cmd      | LCD_Cmd       | iLCD_Cmd→     | 3 bit unsigned integer to<br>start and select the LCD<br>sequencer FSM branch                                |

| 1     | LCD_Data       | →iLCD_Data     | LCD_Data      | LCD_Data→     | 16 bit Command/Data to<br>write to ILI9341 LCD driver                                                        |

| 2     | MA_Cmd         | —iMA_Cmd       | MA_Cmd        | iMA_Cmd→      | 1 bit Command to initiate<br>DMA image read from frame<br>buffer                                             |

| 3     | -              | Don't care     | MA_Status     | iStatus→      | 1 bit Status register, 0: busy.<br>1: ready for the next frame.                                              |

| 4     | MA_FBAddr      | →iFBAddr       | MA_FBAddr     | iFBAddr→      | 32 bit base address of<br>image frame buffer in<br>memory                                                    |

| 5     | MA_FBLgt       | →iFBLgt        | MA_FBLgt      | iFBLgt→       | 32 bit integer for length of<br>image frame buffer.<br>Corresponds to number of<br>words to read from memory |

| 6     | -              | Don't care     | -             | 0x00          |                                                                                                              |

| 7     | -              | Don't care     | -             | 0x00          |                                                                                                              |

## Custom IP register map

Table 1. Register map of the Avalon Slave Memory Mapped Register Interface

## Top-level block diagram Hardware connection

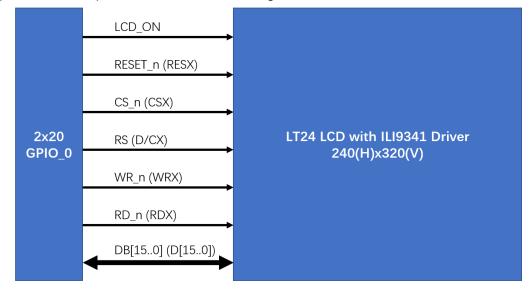

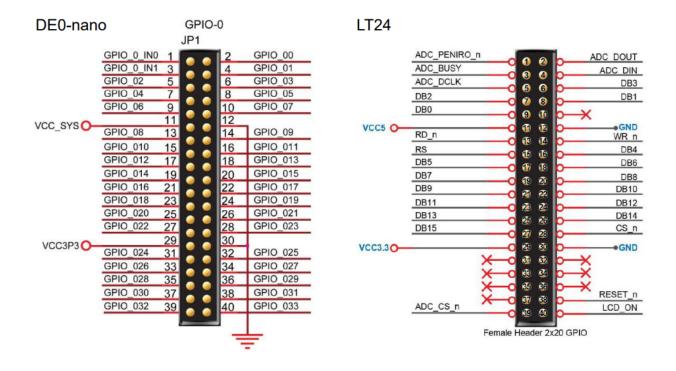

The LT24 camera module will be connected to the GPIO\_0 connector of the DE0 Nano FPGA development board. The connections between the custom *LCD Controller* IP and the development board's pins are detailed in the diagram below:

# **Memory Organization**

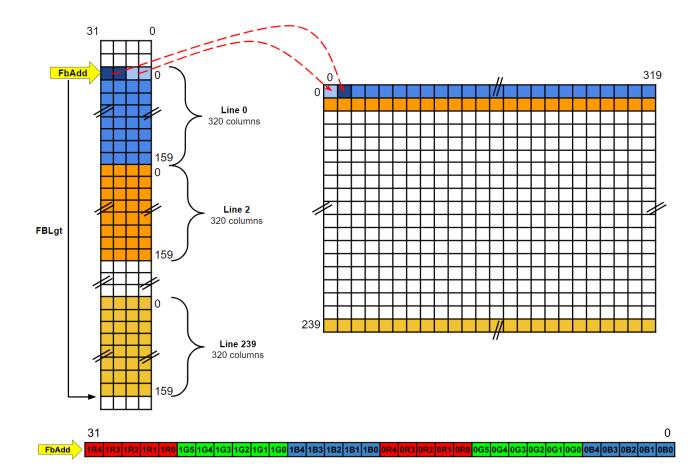

The memory organization paradigm must be agreed upon with the team implementing the complementary camera DMA to ensure interoperability of the two-subsystems. The memory will be organized in a 16-bit, 5-6-5 RGB format. Two pixels will be stored as doublets in one 32b word. The image frame buffer organization as well as the organization of one word (example word shown is the case of pixels 0 & 1 stored in the memory address pointed to by FBAdd).

# LT24 Control

## LT24 Register Initialisation

At the startup of LT24 LCD Display an initialization is needed to set up the parameters of the device. The initialization is done by writing the command address or data to LCD\_Data Register and appropriately setting LCD\_Cmd Register. The written command will be automatically handled by the Finite State Machine of LCD controller and sent to the LT24 chip respecting the protocol and time constraints. The LCD\_ON signal will be permanently routed to 3.3V. The initialization of the LT24 is done as shown in the steps below:

- 1. Set-Reset-Set the Hardware Reset signal RESX to the LT24 module.

- 2. Exit Sleep mode by writing to 0x0011 Command address without data.

- 3. Registers shown in the table below related to power, gamma are configured to the recommended value according to the lecture slides.

- 4. The EC (end column) and EP (end page) values in ILI9341 registers 0x2A and 0x2B are set to 319 and 239 respectively.

- 5. The MACTR register (0x36) is set to 'X-Y Exchange X Mirror' mode.

| Registers                          | Address                              |

|------------------------------------|--------------------------------------|

| Power control                      | 0xC0, 0xCF (Level 1), 0xC1 (Level 2) |

| Power on sequence control          | 0xED                                 |

| Driver timing control              | 0xE8                                 |

| Power control                      | 0xCB                                 |

| Pump ratio control                 | 0xF7                                 |

| Display function control           | 0xB6                                 |

| VCM control                        | 0xC5, 0xC7                           |

| 3-Gamma control                    | 0xF2                                 |

| Gamma-Set                          | 0x26                                 |

| Positive/Negative Gamma Correction | 0xE0, 0xE1                           |

Table 2. Register Initialisation with default values

6. Other Registers are set according to our specific design needs.

| Registers                           | Address    | Details                                                |

|-------------------------------------|------------|--------------------------------------------------------|

| Pixel Format Register               | 0x3A       | MCU Mode I for 5-6-5<br>16bit-RGB parallel<br>transfer |

| Interface Control                   | 0xF6       | Internal-clock mode                                    |

| Memory access control<br>Registers  | 0x36       | Mirror the image with left-top pixel as origin         |

| Column and Page Address<br>Register | 0x2A, 0x2B | Changing the image size from 240*320 to 320*240        |

| Frame rate normal mode control      | 0xCB       | 70Hz according to our writing speed                    |

Table 2. Register Initialisation with default values

### LT24 Data Transfer

After setting up the Registers, the display would be turned on by writing to Display On (0x29). Frame data can be written to the memory after setting the Memory Write Register (0x2C). The

chip-select for the ILI9341 is held low continuously, as stated in the datasheet the device will still operate correctly in parallel interface mode.

# Conclusion

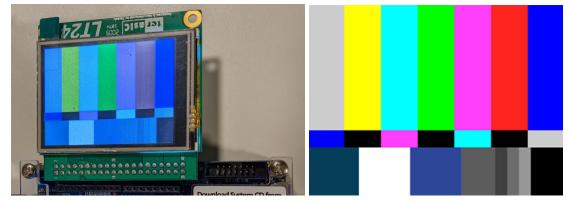

The design specified in Lab 3 was implemented in hardware on a DE0\_Nano Intel FPGA development board with only minor changes and simplifications. After some troubleshooting, the LCD controller subsystem can successfully read an image in the defined format from a specified location in memory and display the contents on the LCD. The display for 1 image takes 12ms, which allows a frame rate of 81Hz.

## References

- 1. Terasic, DE0-Nano-SoC\_User\_manual <u>https://www.intel.com/content/dam/altera-www/global/en\_US/portal/dsn/42/doc-us-dsnbk</u> <u>-42-5804152209-de0-user-manual.pdf</u>

- Terasic, LT24 Datasheet. <u>https://www.terasic.com.tw/cgi-bin/page/archive\_download.pl?Language=English&No=8</u> <u>92&FID=527f33a451f2c9a404934446366f5342</u>

- Terasic, LT24 DE-10 Demonstration <u>https://www.terasic.com.tw/cgi-bin/page/redirect.pl?Url=http%3A%2F%2Fdownload.teras</u> <u>ic.com%2Fdownloads%2Fcd-rom%2Fde10-nano%2Fde10-nano\_db\_demo%2FLT24.zip</u>

- 4. ILI9341 Datasheet: https://cdn-shop.adafruit.com/datasheets/ILI9341.pdf